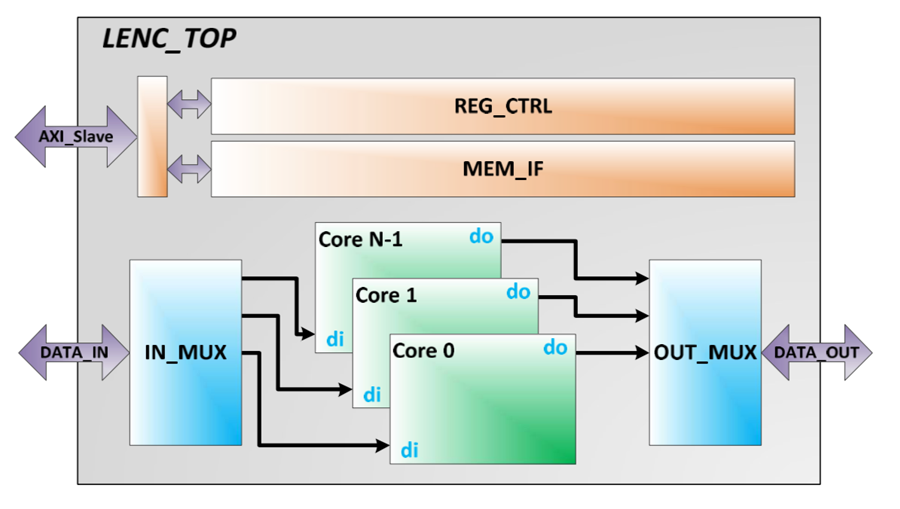

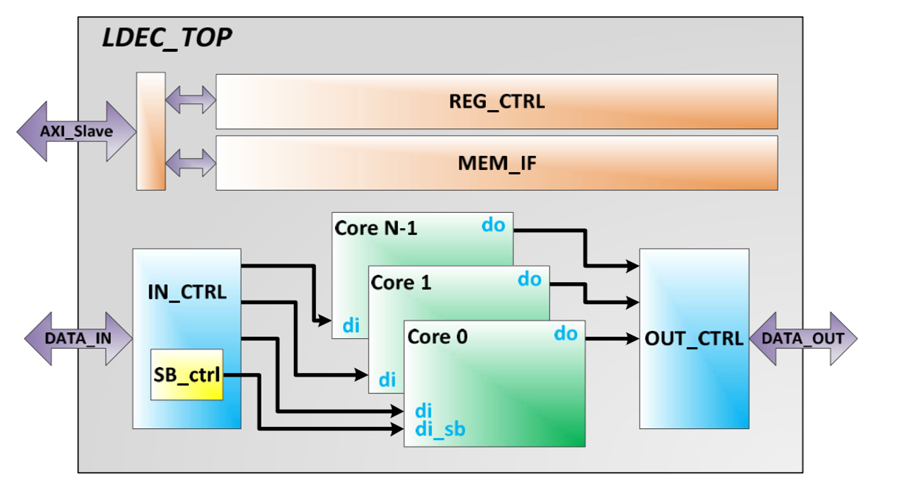

EpoStar’s LDPC IP Core (Alcyone) delivers industry-leading error correction performance to support 2S/3D SLC/MLC/TLC/QLC NAND for each application from mobile, client, and enterprise NAND flash controller markets. Alcyone provides a highly efficient pure hardware engine with standard AXI interface for easily integration.

Based on several patented technology of EpoStar, the Alcyone LDPC IP provides very high throughput and error correction capability with low area and power consumption.

EpoStar’s LDPC IP was silicon-proven in industrial/enterprise SSD, USB, and EMMC application.

+Support 1KB+/2KB+/4KB+ codeword size for one time configuration

+Support code rate (CR) range 0.93~0.83(down to 0.71)

+Support configurable throughput, ranges from 300MB/s to 14GB/s

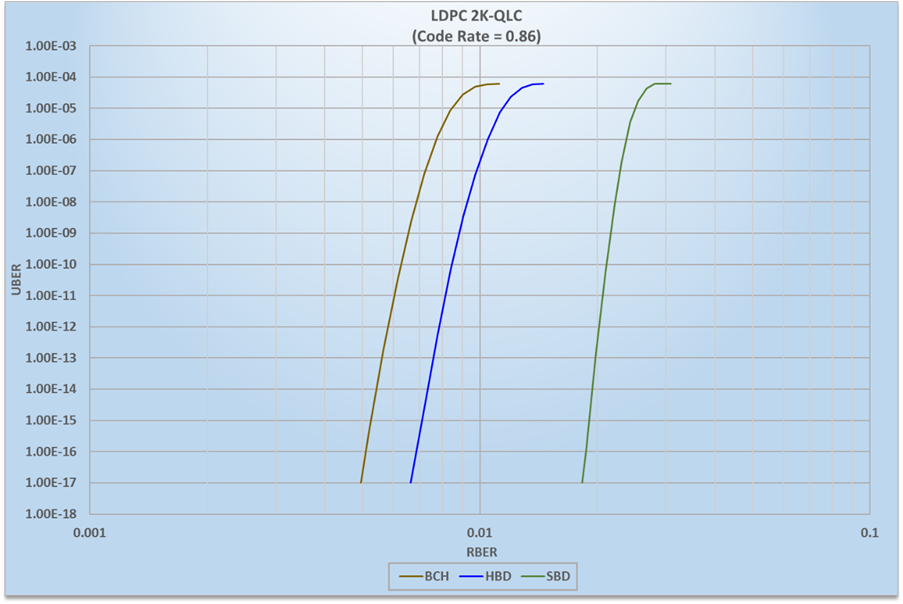

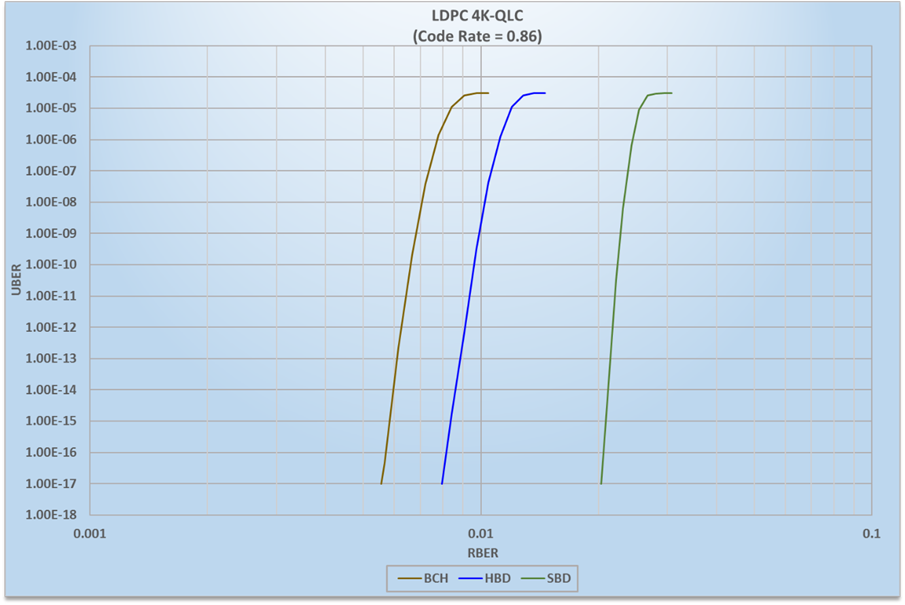

+Support hard-bit decode (HBD) and up to 6bit soft-bit decode (SBD)

+Proven to reach UBER lower than 1E-17 in both HBD and SBD

+Build in low power engine

+Support variable code rate for various 2D/3D SLC/MLC/TLC/QLC NAND flash

+Support byte-by-byte adjustment in user data and parity data area of code rate

+Asynchronous design with 2 clock sources (system and core)

+Support on-the-fly dynamic code rate swapping

+Support on-the-fly error bit reporting

+Support early termination mechanism

+Support configurable termination condition

+Qualified with AWGN channel model platform and real NAND flash platform

+RTL code

+Sanity check RTL simulation environment

+Synthesis script for ASIC and FPGA

+LDPC encoding/decoding C library

+LDPC encoding/decoding matrices

+NAND flash LLR LUT calibration utility

+Documentations

+Training Course