+Compliant to NVMe 1.4 specifications

+Support up to 256 functions for SRIOV or physical functions

+Support up to 512 namespaces

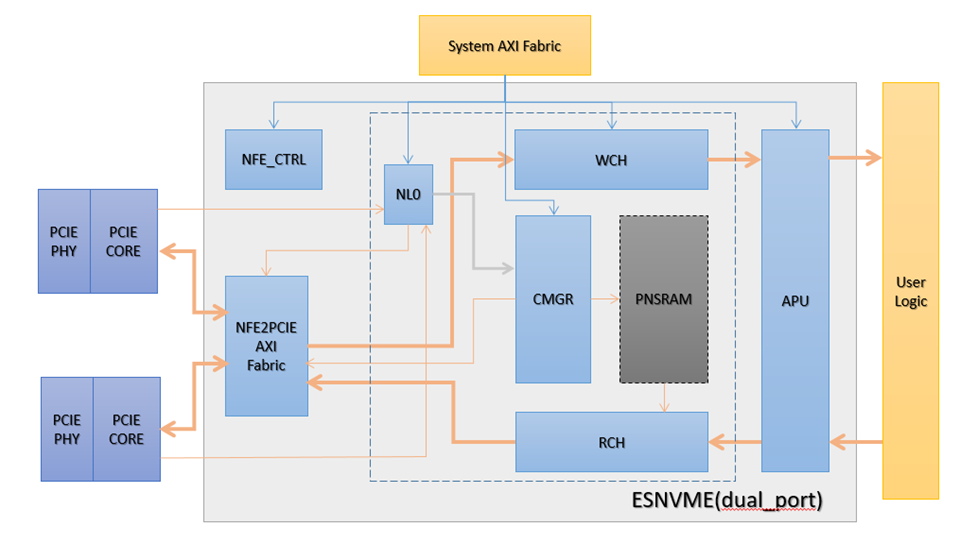

+Support dual ports

+Support up to 512 queue pairs

+Support up to 4096 outstanding commands

+Maximum 64K submission queues entries per submission queue

+Maximum 64K completion queues entries per completion queue

+Support out-of-order IO read data from flash to host

+Support out-of-order IO write command execution

+Support Metadata Pointer (MPTR) for +8 and +16

+Support IO determination

+Weighted round robin with urgent priority class command arbitration

+Support PRP and SGL IO command sets

+Support E2E data and control path protection

+Maximum memory page size of 64KB

+Minimum memory page size of 4KB

+Support Host Memory Buffer (IP provides extra AXI port for SSD system to access PCIe bus)

+Support T10-DIF

+Support MSI, MSI-X, and legacy interrupt

+Support interrupt coalescing

+Support LBA size 512B, 4096B

+Support HMB

+Support CMB

+Support PCIe Dual port

+Pass UNH-IOL compliance test

+RTL code for both ASIC and FPGA

+Verilog direct test verification environment

+Synthesis script for Synopsys Design Compiler and Xilinx FPGA

+NVMe reference firmware

+Documentation

● Datasheet

● Integration guide

● Register specification

● Firmware programming guide